# Arithmetic logic units and memory

# Layers of abstraction

| abstraction           | building blocks                                    | examples                             |

|-----------------------|----------------------------------------------------|--------------------------------------|

| computer              | components                                         | Macbook Pro                          |

| components            | multiplexer,<br>demultiplexer, adder,<br>flip-flop | registers, ALU, counter              |

| sequential circuits   | logic gates, connectors, clock                     | flip-flop                            |

| combinational circuit | logic gates, connectors                            | multiplexer,<br>demultiplexer, adder |

| logic gates           | switches, connectors                               | AND, OR, NOT                         |

| clock                 | raw materials                                      | crystal oscillator                   |

| connector             | raw materials                                      | Wire                                 |

| switch                | raw materials                                      | transistor, relay                    |

#### **ALU**

- ALU (Arithmetic Logic Unit)

- Building block of the CPU

- Normally at least:

- Bitwise AND, NOT, OR, XOR

- Integer addition, subtraction

- Bit shifting

- Input from memory register(s)

- Output to memory register

- Which operation stored determined by signal from control unit

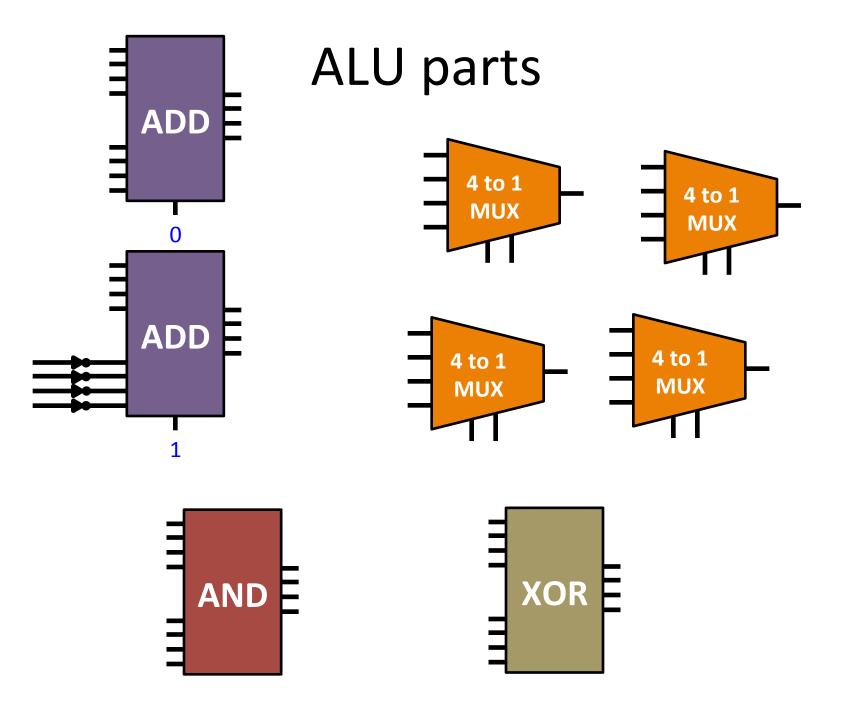

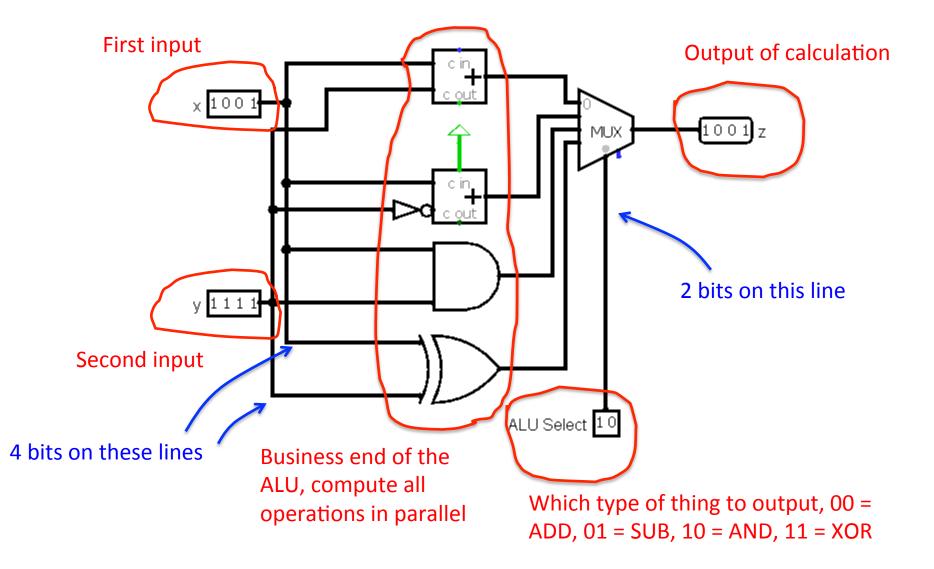

#### Let's build an ALU

- ALU (Arithmetic Logic Unit)

- 4 different operations

- Add, subtract, bitwise AND, bitwise XOR

- Two 4-bit inputs

- One 4-bit output

- ALU performs all 4 operations in parallel

- 2 selection bits select result put on output wires

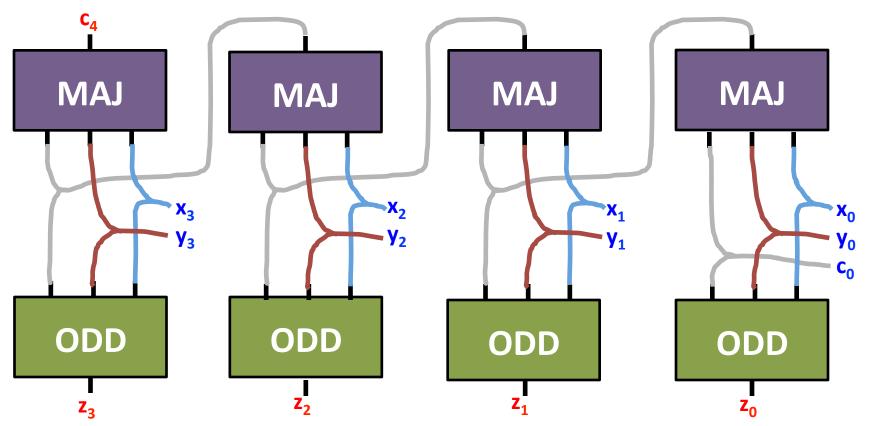

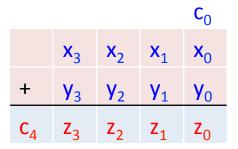

#### 4-bit full adder

• Goal: x + y = z for 4-bit integers

|                |                       |                       |                       | $c_0$                 |

|----------------|-----------------------|-----------------------|-----------------------|-----------------------|

|                | <b>X</b> <sub>3</sub> | <b>X</b> <sub>2</sub> | <b>x</b> <sub>1</sub> | $\mathbf{x}_0$        |

| +              | <b>y</b> <sub>3</sub> | <b>y</b> <sub>2</sub> | <b>y</b> <sub>1</sub> | <b>y</b> <sub>0</sub> |

| C <sub>4</sub> | $z_3$                 | <b>Z</b> <sub>2</sub> | <b>Z</b> <sub>1</sub> | $z_0$                 |

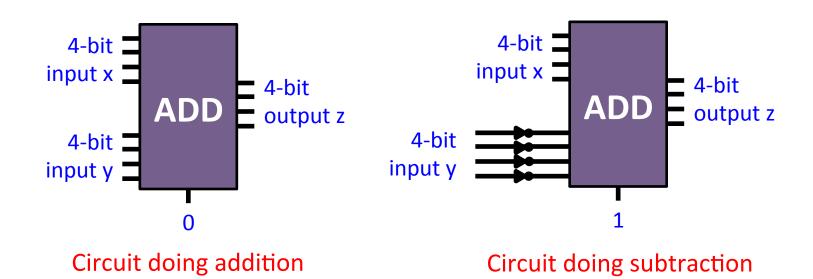

#### 4-bit adder

#### 4-bit subtractor

- Goal: x y = z for 4-bit integers

- One approach: design like adder circuit

- Better approach: reuse the adder

- Two's complement, invert bits and add 1

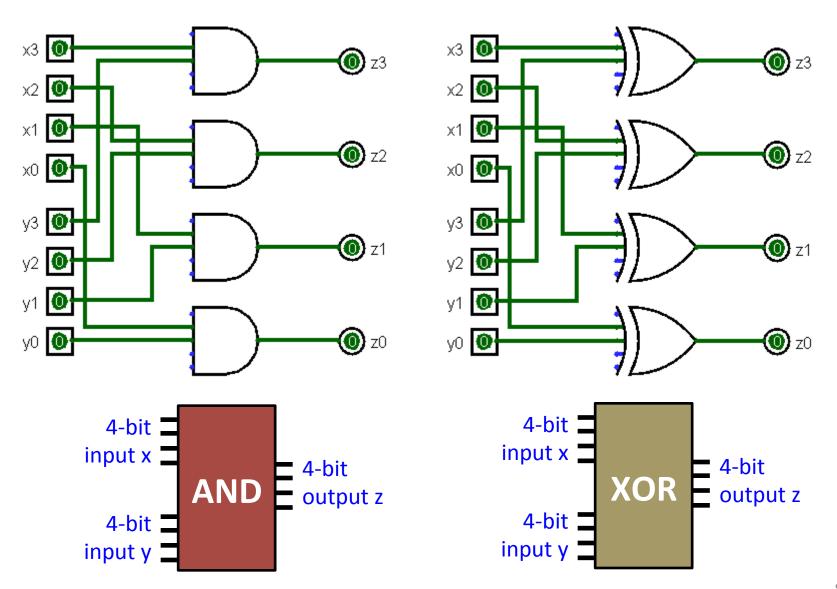

#### Bitwise AND, XOR

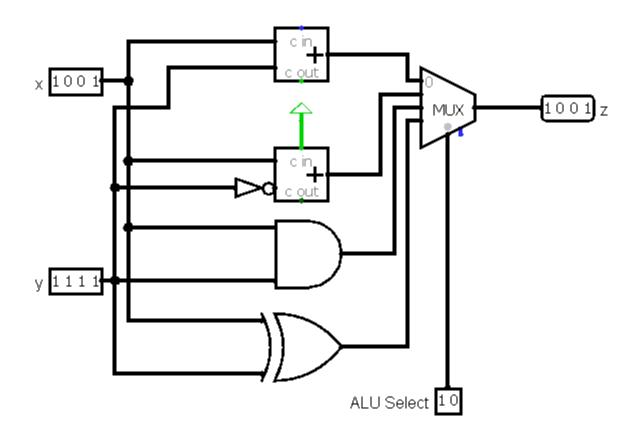

#### ALU with 4-bit lines

#### Our simple ALU

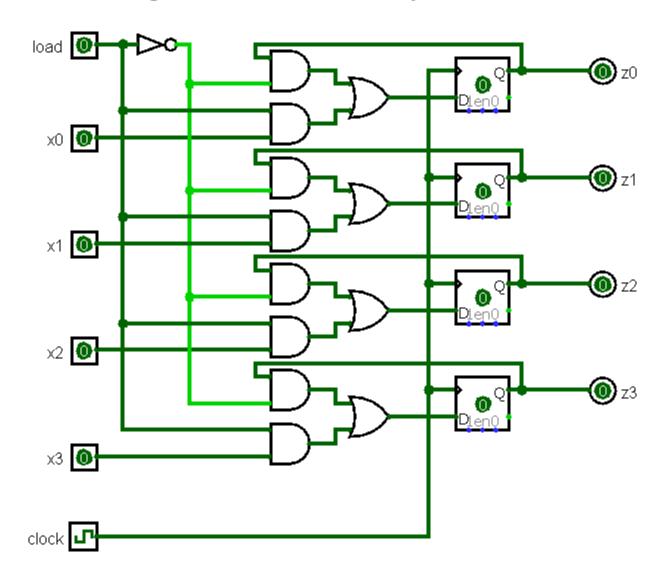

## Let's build a register

- n-bit register

- Group of n flip-flops storing n bits

- Includes combinational gates

- Provides output of its n stored bits

- Can be told to memorize n bits on input lines

- Someone sets load line high

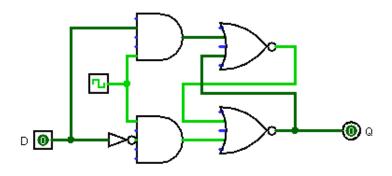

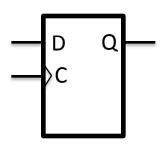

#### Clocked D flip-flop

- D flip-flop

- Hook the enable line to a clock

- Clocked latch = flip-flop

- State change has to wait for next clock cycle

| D (data) | C (clock) | Q(t) | Q(t+1) |

|----------|-----------|------|--------|

| 0        | high      | X    | 0      |

| 1        | high      | X    | 1      |

# 4-bit register with parallel load

4-bit register with parallel load Set to high load 💇 to memorize input bits х0 🕡 **0** 0 Input bits **(** x2 💽 **( Output bits** Logic to keep value the same except if load is high Flip-flops

clock 🗗

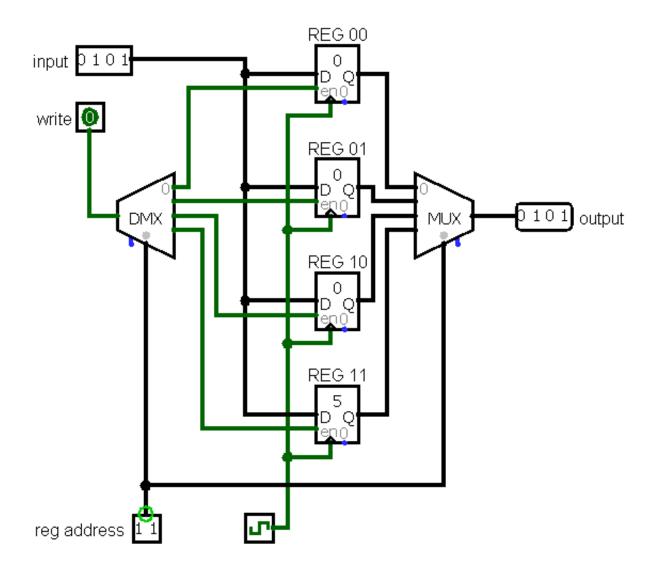

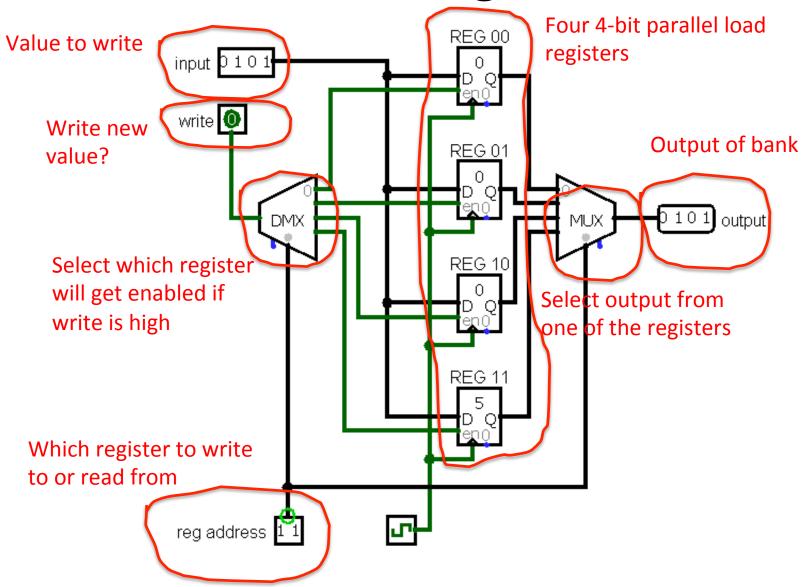

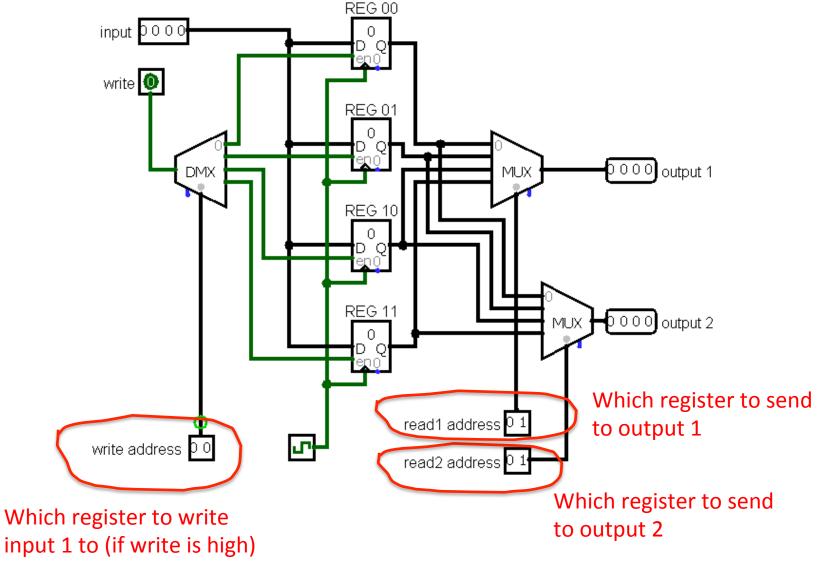

#### Let's build a register bank

- We need to store multiple variables

- Use four 4-bit registers

- Someone sets target register number 0-3

- Put target register's stored value on output line

- If write bit enabled, make target register memorize data on input line

# Four 4-bit register bank

#### Four 4-bit register bank

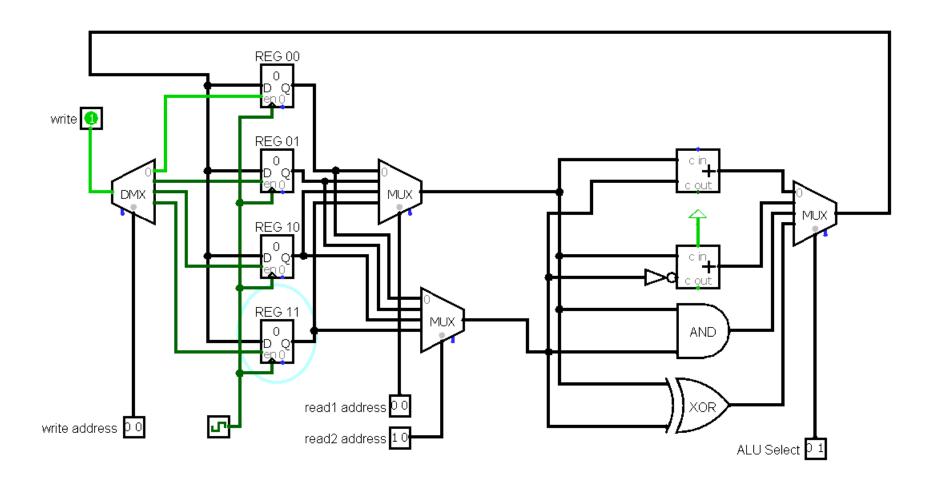

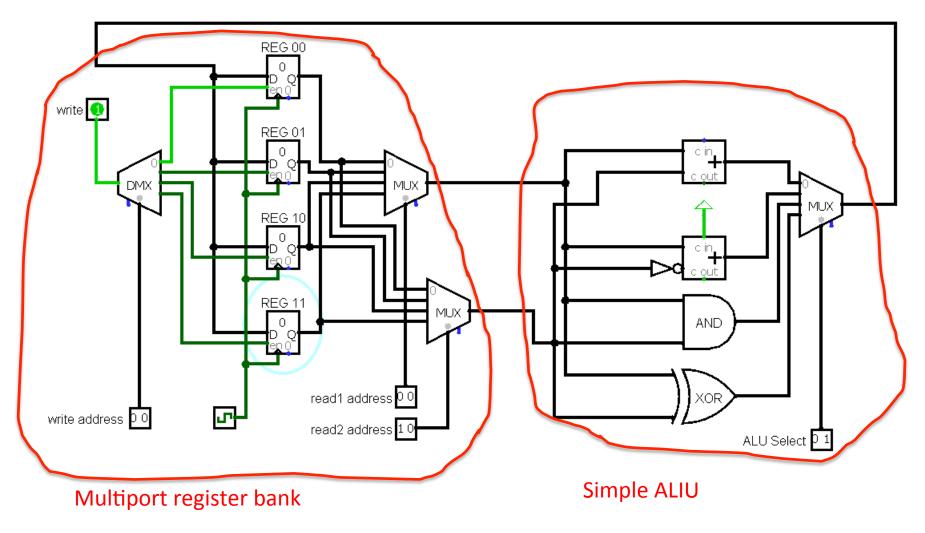

## Let's build a computer (sort of)

- So far we've built:

- ALU

- Computes 4 operations on two 4-bit numbers

- Register bank

- Select one of four 4-bit numbers

- Let's hook them together!

- Problem: ALU needs two inputs and one output

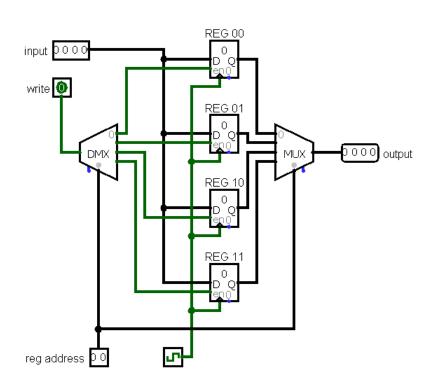

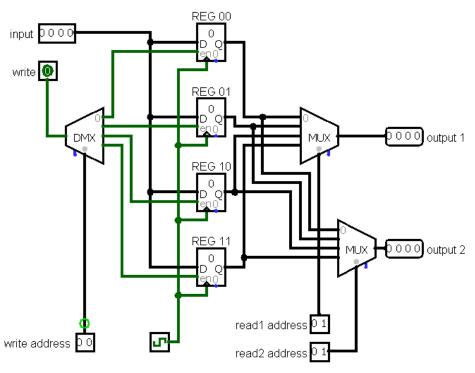

#### Multiport register bank

Original design of register bank

New design, can write to one address while reading from two different addresses

#### Multiport register bank

# Hello computer

## Hello computer

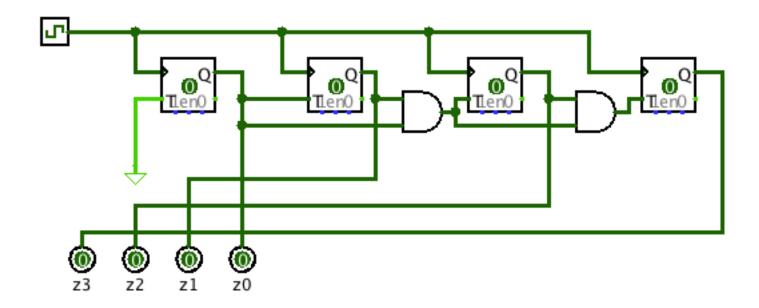

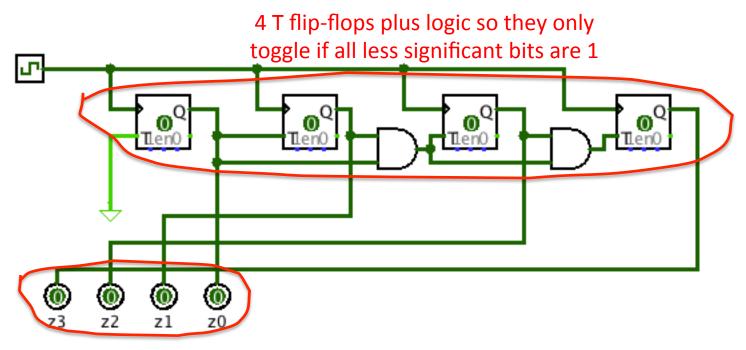

#### Let's build a counter

- 4-bit synchronous counter

- Count from 0000 up to 1111

- Roll back to 0

- Increment on each clock cycle

- Working on an algorithm

- Which bit always flips?

- When do other bits flip?

| Counter |

|---------|

| 0000    |

| 0001    |

| 0010    |

| 0011    |

| 0100    |

| 0101    |

| 0110    |

| 0111    |

| 1000    |

| 1001    |

| 1010    |

| 1011    |

| 1100    |

| 1101    |

| 1110    |

| 1111    |

#### Let's build a counter

- 4-bit synchronous counter

- Count from 0000 up to 1111

- Roll back to 0

- Increment on each clock cycle

- Working on an algorithm

- Which bit always flips?

- Least significant bit always flips

- When do other bits flip?

- Other bits flip when all bits to right are 1

| Counter |

|---------|

| 0000    |

| 0001    |

| 0010    |

| 0011    |

| 0100    |

| 0101    |

| 0110    |

| 0111    |

| 1000    |

| 1001    |

| 1010    |

| 1011    |

| 1100    |

| 1101    |

| 1110    |

| 1111    |

## JK flip-flop

- JK flip-flop

- Refinement of SR flip-flop

- SET: J=1, K=0

- RESET: J=0, K=1

- TOGGLE: J=1, K=1 (flips the stored bit)

| J | К | C (clock) | Q(t) | Q(t+1) |

|---|---|-----------|------|--------|

| 0 | 0 | high      | x    | x      |

| 0 | 1 | high      | x    | 0      |

| 1 | 0 | high      | x    | 1      |

| 1 | 1 | high      | X    | x'     |

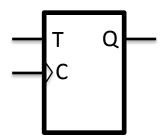

## T flip-flop

- T flip-flop "toggle"

- Like JK but connect J and K together

- LEAVE: T=0

- TOGGLE: T=1 (flips the stored bit)

| Т | C (clock) | Q(t) | Q(t+1) |

|---|-----------|------|--------|

| 0 | high      | Х    | x      |

| 1 | high      | X    | x'     |

# 4-bit synchronous counter

## 4-bit synchronous counter

4-bit output of counter

#### Summary

- Built a simple ALU

- Used flip-flops to build a register

- Created a register bank

- Created a multiported register bank

- Made a simple computer

- Made a counter